# Isolated Control A/D Module 57409

# Features

Two input channels ±1V or =10V input ranges 12-bit conversion plus polarity 100% overrange capability 500V isolation between inputs and log in Software selectable input filtering Software settable sampling rates Constant clock (CGLK) Interrupt capability Precision valtage source for potentiometers Usable intal Main Rack or Remote Rack

# Function

The Iso ated Control A/D Module provides for input to the Distributed Control System (DCS) of voriable D-C reference or reedback's ghats for high portprimates closed loop control. It can also be used as a general purpose input for analog signals that are less time-chiridal.

## Mechanical Description

The isolated Control A/D Module is a printed direct board assembly that plugs into the Multipus\* backplane of the DOS Pack. It consists of the printed circuit board, a faceplate, and a protective endosure. The assembly dimensions are listed under "Technical Specifications."

The faceplate of the module centa as a P3 female connector socket. External signals are connected to this socket via a supplied multipunductor pable with an attached 10-point terminal board plug. The accket and plug are keyed to prevent insertion of the cable plug, into the wrong module.

Also on the laceplate are four LED indicators. The top two LEDs indicate that CCLK is on and that CCLK is enabled from this module. The lower LEDs are for factory testing.

The standard connectors that interface with the system. Multibus are at the back of the module

# **Electrical Description**

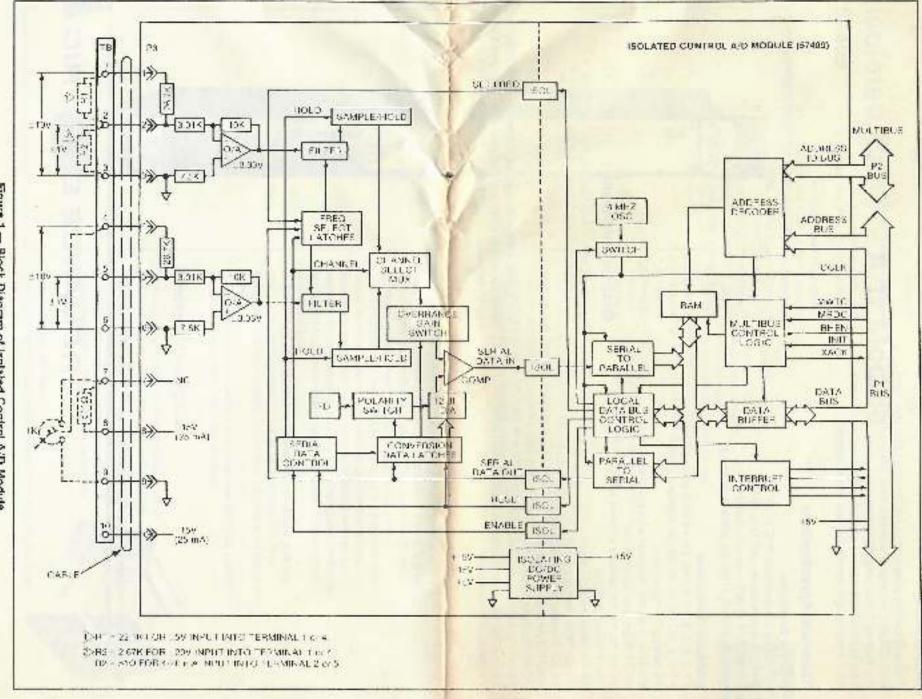

The circuitry in the module is divided into two sections, the isolated mout circuits and the digital logicid routls. The two sections are connected by two obtical solators and a DC-to-BC isolated power supply. A plock diagram of this circuitry is shown in Figure 1

## Isolated Input Section

Input scaling amplifiers are designed for = /2 mA input for

RELIANCE ELECTRIC

PROFESSION AND

Relience\* Distribute Control System

followeally conversion to  $\pm 4695$ . Resistors are provided on the PC board for inputs of  $\pm 10$  value or  $\pm 1$  value for 1 scale. Other inputs can be accommodated by connecting resistors to the terminal board as shown. The PC board resistors are rated at  $\frac{1}{2}$  watt.

Low bass filters with addiware selectable bandwith is smooth out transients and also provide anti-aliasing for signals with high frequency components. The two-pole filtors have a damping factor of 175 with corner fimulencies (90-degree chase shift) listed under Programming "

Sample-and-hold circuits maintain constant input values during conversion. A multiplexer selects the channel to be converted.

A gain switch reduces the gain between the input signal and the successive approximation comparator when the signal exceeds the nominal input value. When in this over range condition inconversion accuracy is degraded and there may also be a discontinuity during the transition Thus, the overrange should only be used to detect shnormat signal revels. (Maximum overrange converts to #6191.)

A propision voltage source provides the reference signal for the successive approximation digital-to-analog convertor. Reference polarity is switched for negative input sighals to provide the full 12 bit conversion in either polarity. The inverted gain is factory adjusted to make the positive and negative references equal in magnitude. The output of the D/A convertor is compared with the input signal as each bit is tested in descending order outing the successive sporoximation conversion routing.

Latches are used to store serial data from the digital logic section and convert if to the parallel data required for the filter solution and for the DrA sources of .

#### Digital Logic Section

The Multibus interface is similar to all other DCS modules. The module sign floation is identified by module address ID lines on P2. On receipt of a memory read or memory write signs from a Processor Module, the module and regster address lines are decoded, and data is transferred between the Multibus data lines and one of the eleven registers of onboard memory. A transfer addressing up, control are storug to the Processor. Upon powering up, control and storug registers are set to zero by the initial zo or board reset signal but not the data registers. The control and data register definitions are listed under "Programming."

This module contains a 4 MHz clock that can be used as the Multibus constant clock (CCLK). Whether or not it is used is determined by a software settable control bit. Only one CCLK can be enabled in a rack. This must be done after the filter frequency is selected and the update period is set on all isolated Control A/D Modules in the rack and after similar registers are set on all other mudules that use CCLK

The CCLK signal is divided by form to produce a 1 MHz signal for timing the successive approximation conversion, it is further divided to produce a signal (HK) every 500 microseconds that initiates a conversion cycle for both input signals or causes the litter selection to be updated on either or both channels if changed

The local bus control includes the functions of update period countors for each channel. When the CCLK is enabled, the value in the preset count my sterior local memory for each channel is transferred to the respective ourrent count register. At each 500 microsecond TIK's ghall each current count register is decremented by one count. When either register reaches zero, the latest input value for that channel is transferred to the respective input data register, and the current count is reset to the preset value. This can also generate an interrupt to the Processon Modure if programmed to do so.

If the presel bount register is set to one, the input data register will be updated every 500 microseconds. This is the normal mode of operation if the interrupts are not used.

The interrupt onlivers are onabled by an event definition statement in the software lask that reads the input channel. When the event is defined, the operating system assigns it an interrupt line and identifies the module and channel that drives it. There can be up to four possible I/O interrupt sources defined on a rack.

## Programming

The software required to use an Isolated Control A/O Module consists primarily of defining a logical variable name for each register used, then reading or setting the values of the variables. If the interrupt function is used, there must also be a hardware event definition statement. The variable names and their physical addresses are assigned in the configuration task in IODEF or RIODEF statements. The logical names must also be declared as COMMON variables in each application task that refers to them.

Inclated Control A/D Module registers are defined below. Indefined bits autor are not used or sto for manufacturing test porposes only. Values must diways be assigned to registers 7, a, 9, and 10 before the CCLK is enabled. Registers 0 through 4 are read only; all inhers are read/write. To huron the CCLK on a particular module, bit 6 of both registers 5 and 6 of the module must be set true by one of the applcation tasks. The application tasks can read the status of the CCLK from bits 6 and 8 in redister 4.

| Register 0: Channel 1 converted input data                 |

|------------------------------------------------------------|

| Register 1: Channel 2 converted input cala                 |

| Register 2: Channel 1 purrent count of update pariod       |

| Register & Channel 2 purrent count of update period        |

| Register 4: Read unly status                               |

| Bit 6 - CCLK enabled                                       |

| Bits 8, 10 - CCLK on                                       |

| Regiour & Channel 1 Interrupt control register             |

| Bits C. 1 - Interruct Inc. D                               |

| Bil 2 - Interrupt allocatori                               |

| Bild - CCLK enable                                         |

| 24.7 - Interrupt enabled                                   |

| Bit 15 - Interrupt device flag                             |

| Peolster 5: Channel 2 interniblicantrol register: same as  |

| registor 5                                                 |

| Register /: Channel 1 update period preset count           |

| Register A: Channel 2 update period proset count           |

| Register 9: Channel 11 iter selection                      |

| 0 = 300 rad/sec                                            |

| 1 - 145 rad/sec                                            |

| 2 - 79 rad/sec                                             |

| 0 - 21 rad/sec                                             |

| Pegister 10: Chennel 2 filter selection/seme as register 9 |

|                                                            |

Figure 1-Block Diagram of Isolated Control A/D Module

34

# Diagnostics

The only built-in diagnostics are the two LEDs that indicate CCLK is on and/or chabled from this module. To test the module, first check the isolated power supply outputs, then connect appropriate signals to the inputs and use e CRT Programmento monitor and force registers.

## **Technical Specifications**

#### Ambient Conditions

Coerating temperature: 0° C to 55° C Storage temperature = 40° C to 55° C Humidity: 5 to 90% non-condensing Altitude: 0300 II. (1000 m) without derating

## Backplane Connections

F1-5, 4, 5, 6, 31, 82, 83, 84; -5VD-C at 4 82A max P1-1, 2, 11, 12, 75, 76, 85, 56; Signal common P1-59 thru 74: Data Lines P1-43 thru bè, 58: Register address lines. P1-57: High ovte address line P1-28, 38, 32, 34: Module address lines. P1-14: initialize input P1-19: Read memory input P1-20: Write memory input P1-23. Transfer acknowledge output P1-27 Byle high enable input P1-31, Censlant clock (OCLK) P1-39, 40, 41, 42: Interrupt lines. P2-5 9 10 14 Module address identif pation lines P2-38. Board reset input P2-39: System watchdog rimer OK input

Maximum Module Dissipation 25 write

## Isolated Power Supply Output: +16V and =15V at 25 mA each Accuracy: =1% at 0 to 25 mA Thermal dr It: = 01% per degree C

### Conversion Performance

(Values given in % of full scale, ±1/, bit) Nominal Absolute Accuracy, ±10,000V \_2% = ±4095 Repeatability: 1 LSB = .25% Lineanity: ±.025% Thermal drift: .015% per degree C Offset: = 79mV to ..55mV max Update period. 500 µsec to 32,7075 sec

## Dimensions

Height, 11%," Width, 1%," Deeth, 7%,"

# **Ordering Information**

faulated Control A/D Modulo: Part No. 57409 Terminal Epard and Capiol Part No. 612117-R

For further information about the Reliance Electric Distributed Control System, contact your local Reliance Electric Sales Office or call toll free 1-800-245-4501. (In Ohio call 1-800-245-4497.)

Reliance Electric Company / 24703 Euclid Avenue / Cleveland, Ohio 44117